D/A CONVERTERS

# AD7541

December 1993

# 12-Bit Multiplying D/A Converter

#### **Features**

- 12-Bit Linearity 0.01%

- · Pretrimmed Gain

- · Low Gain and Linearity Tempcos

- Full Temperature Range Operation

- · Full Input Static Protection

- TTL/CMOS Compatible

- . +5V to +15V Supply Range

- · 20mW Low Power Dissipation

- Current Settling Time 1µs to 0.01% of FSR

- · Four Quadrant Multiplication

## Description

The AD7541 is a monolithic, low cost, high performance, 12-bit accurate, multiplying digital-to-analog converter (DAC).

Harris' wafer level laser-trimmed thin-film resistors on CMOS circuitry provide true 12-bit linearity with TTL/CMOS compatible operation.

Special tabbed-resistor geometries (improving time stability), full input protection from damage due to static discharge by diode clamps to V+ and ground, large  $l_{OUT1}$  and  $l_{OUT2}$  bus lines (improving superposition errors) are some of the features offered by Harris AD7541.

Pin compatible with AD7521, this DAC provides accurate four quadrant multiplication over the full military temperature range.

## Ordering Information

| PART NUMBER NONLINEARITY |                                     | TEMPERATURE RANGE | PACKAGE             |  |

|--------------------------|-------------------------------------|-------------------|---------------------|--|

| AD7541AD                 | 0.02% (11-Bit)                      | -25°C to +85°C    | 18 Lead Plastic DIP |  |

| AD7541BD                 | 0.01% (12-Bit)                      | -25°C to +85°C    | 18 Lead Plastic DIP |  |

| AD7541JN                 | 0.02% (11-Bit)                      | 0°C to +70°C      | 18 Lead Plastic DIP |  |

| AD7541KN                 | 0.01% (12-Bit)                      | 0°C to +70°C      | 18 Lead Plastic DIP |  |

| AD7541LN                 | 0.01% (12-Bit) Guaranteed Monotonic | 0°C to +70°C      | 18 Lead Plastic DIP |  |

| AD7541SD                 | 0.02% (11-Bit)                      | -55°C to +125°C   | 18 Lead Plastic DIP |  |

| AD7541TD                 | 0.01% (12-Bit)                      | -55°C to +125°C   | 18 Lead Plastic DIP |  |

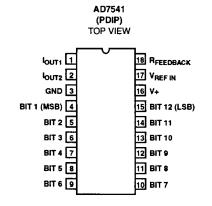

## Pinout

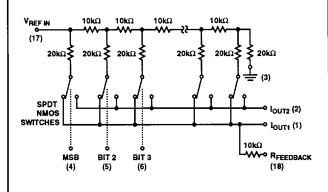

# Functional Diagram

Switches shown are for Digital Inputs "High"

# Specifications AD7541

####

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### Electrical Specifications V+ = +15V, V<sub>REF</sub> = +10V, V<sub>OUT1</sub> = V<sub>OUT2</sub> = 0V, T<sub>A</sub> = +25°C, Unless Otherwise Specified

| PARAMETER                                                     |                         | TEST CONDITIONS                                                                                  | T <sub>A</sub> +25°C             |                |           | TA MIN-MAX |             |                      |

|---------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------|----------------------------------|----------------|-----------|------------|-------------|----------------------|

|                                                               |                         |                                                                                                  | MIN                              | TYP            | MAX       | MIN        | MAX         | UNITS                |

| SYSTEM PERFORMAN                                              | ICE                     |                                                                                                  |                                  |                |           |            | <del></del> |                      |

| Resolution                                                    |                         |                                                                                                  | 12                               |                | -         | 12         | -           | Bits                 |

| Nonlinearity                                                  | A, S, J                 | -10V ≤ V <sub>REF</sub> ≤ +10V                                                                   | -                                | -              | ±0.024    | -          | ±0.024      | % of FSR             |

|                                                               | В, Т, К                 | V <sub>OUT1</sub> = V <sub>OUT2</sub> = 0V<br>See Figure 3                                       |                                  |                | ±0.012    | -          | ±0.012      | % of FSR             |

|                                                               | L                       | (Note 4)                                                                                         |                                  | -              | ±0.012    | -          | ±0.012      | % of FSR             |

| Monotonicity                                                  |                         |                                                                                                  |                                  |                | Guarantee | d          | •           |                      |

| Gain Error                                                    |                         | -10V ≤ V <sub>REF</sub> ≤ +10V (Note 4)                                                          | i -                              | -              | ±0.3      | •          | ±0.4        | % of FSR             |

| Output Leakage Curren<br>(Either Output)                      | t                       | $V_{OUT1} = V_{OUT2} = 0$                                                                        | -                                | -              | ±50       | •          | ±200        | nA                   |

| DYNAMIC CHARACTE                                              | RISTICS                 | <u> </u>                                                                                         |                                  |                | <u> </u>  |            | <del></del> |                      |

| Power Supply Rejection                                        | ì                       | V+ = 14.5V to 15.5V<br>See Figure 5, (Note 4)                                                    | -                                | -              | ±0.005    | •          | ±0.01       | % of FSPV% of<br>ΔV+ |

| Output Current Settling                                       | Time                    | To 0.1% of FSR<br>See Figure 9, (Note 5)                                                         | -                                |                | 1         | -          | 1           | μs                   |

| Feedthrough Error                                             |                         | V <sub>REF</sub> = 20V <sub>PP</sub> , 10kHz<br>All Digital Inputs Low<br>See Figure 8, (Note 5) | -                                |                | 1         | -          | 1           | mV <sub>P-P</sub>    |

| REFERENCE INPUTS                                              |                         | <u> </u>                                                                                         |                                  |                |           |            |             |                      |

| Input Resistance                                              |                         | All Digital Inputs High IOUT1 at Ground                                                          | 5                                | 10             | 20        | 5          | 20          | kΩ                   |

| ANALOG OUTPUT                                                 |                         | Ι, .                                                                                             |                                  | Ļ              |           |            |             | •                    |

| Voltage Compliance Both Outputs, See Maximum Ratings (Note 6) |                         | -100mV to V+                                                                                     |                                  |                |           |            |             |                      |

| Output Capacitance C <sub>OUT1</sub>                          | All Digital Inputs High |                                                                                                  |                                  | 200            | -         | 200        | pF          |                      |

|                                                               | C <sub>OUT2</sub>       | See Figure 7, (Note 5)                                                                           |                                  | -              | 60        | -          | 60          | pF                   |

|                                                               | Couts                   | All Digital Inputs Low)                                                                          | ·                                | ·              | 60        |            | 60          | pF                   |

|                                                               | C <sub>OUT2</sub>       | See Figure 7, (Note 5)                                                                           | •                                | ·              | 200       | -          | 200         | pF                   |

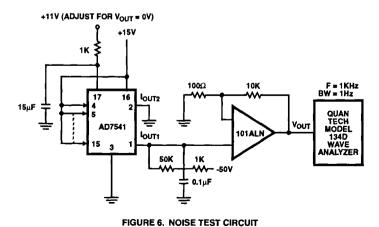

| Output Noise (Both Outputs)                                   |                         | See Figure 6                                                                                     | Equivalent to 10kΩ Johnson Noise |                |           |            |             |                      |

| DIGITAL INPUTS                                                |                         |                                                                                                  |                                  |                |           |            |             |                      |

| Low State Threshold, V                                        | iL                      | (Note 1, 5)                                                                                      | -                                |                | 0.8       | · ·        | 0.8         | V                    |

| High State Threshold, VIH                                     |                         | 1                                                                                                | 2.4                              | <del>  .</del> | -         | 2.4        | † :         | v                    |

## Specifications AD7541

### Electrical Specifications V+ = +15V, V<sub>REF</sub> = +10V, V<sub>OUT1</sub> = V<sub>OUT2</sub> = 0V, T<sub>A</sub> = +25°C, Unless Otherwise Specified (Continued)

| <del></del>                |                                                           |     | T <sub>A</sub> +25°C |             | T <sub>A</sub> MI | N-MAX | _     |

|----------------------------|-----------------------------------------------------------|-----|----------------------|-------------|-------------------|-------|-------|

| PARAMETER                  | TEST CONDITIONS                                           | MIN | ТҮР                  | MAX         | MIN               | MAX   | UNITS |

| Input Current              | V <sub>IN</sub> = 0V or V+ (Note 5)                       | -   |                      | ±1          | •                 | ±1    | μА    |

| Input Coding               | See Tables 1 & 2 (Note 5)                                 |     | Bina                 | ry/Offset B | inary             |       |       |

| Input Capacitance          | (Note 5)                                                  |     | -                    | 8           | •                 | 8     | pF    |

| POWER SUPPLY CHARACTERI    | STICS                                                     |     |                      |             |                   |       |       |

| Power Supply Voltage Range | Accuracy is not guaranteed over this range                |     |                      | +5 to +16   |                   |       | ٧     |

| l+                         | All Digital Inputs High or Low (Excluding Ladder Network) | -   | •                    | 2.0         |                   | 2.5   | mA    |

| Total Power Dissipation    | (Including Ladder Network)                                |     | 20                   |             | -                 | -     | mW    |

#### NOTES:

- The digital control inputs are zener protected; however, permanent damage may occur on unconnected units under high energy electrostatic fields. Keep unused units in conductive foam at all times.

- 2. Do not apply voltages higher than VDD or less than GND potential on any terminal except VREF and RFEEDBACK.

- 3. Full scale range (FSR) is 10V for unipolar and ±10V for bipolar modes.

- 4. Using internal feedback resistor, RFEEDBACK-

- 5. Guaranteed by design or characterization and not production tested.

- 6. Accuracy not guaranteed unless outputs at ground potential.

#### Definition of Terms

**Nonlinearity:** Error contributed by deviation of the DAC transfer function from a "best fit straight line" function. Normally expressed as a percentage of full scale range. For a multiplying DAC, this should hold true over the entire V<sub>REF</sub> range.

**Resolution:** Value of the LSB. For example, a unipolar converter with n bits has a resolution of LSB =  $(V_{REF})/2^{-N}$ . A bipolar converter of n bits has a resolution of LSB =  $(V_{REF})/2^{-(N-1)}$ . Resolution in no way implies linearity.

Settling Time: Time required for the output function of the DAC to settle to within  $^{1}/_{2}$  LSB for a given digital input stimulus, i.e., 0 to Full Scale.

Gain Error: Ratio of the DAC's operational amplifier output voltage to the nominal input voltage value.

Feedthrough Error: Error caused by capacitive coupling from  $V_{\mathsf{REF}}$  to output with all switches OFF.

Output Capacitance: Capacitance from  $I_{OUT_1}$ , and  $I_{OUT_2}$  terminals to ground.

Output Leakage Current: Current which appears on I<sub>OUT1</sub>, terminal when all digital inputs are LOW or on I<sub>OUT2</sub> terminal when all inputs are HIGH.

## **Detailed Description**

The AD7541 is a 12-bit, monolithic, multiplying D/A converter. A highly stable thin film R-2R resistor ladder network and NMOS SPDT switches form the basis of the converter circuit. CMOS level shifters provide low power TTL/CMOS compatible operation. An external voltage or current reference and an operational amplifier are all that is required for most voltage output applications. A simplified equivalent circuit of the DAC is shown on page 1, (Functional Diagram). The NMOS SPDT switches steer the ladder leg currents between I<sub>OUT1</sub> and I<sub>OUT2</sub> buses which must be held at ground potential. This configuration maintains a constant current in each ladder leg independent of the input code. Converter errors are further eliminated by using wider metal interconnections between the major bits and the outputs. Use of high threshold switches reduces the offset (leakage) errors to a negligible level.

Each circuit is laser-trimmed, at the wafer level, to better than 12-bits linearity. For the first four bits of the ladder, special trim-tabbed geometries are used to keep the body of the resistors, carrying the majority of the output current, undisturbed. The resultant time stability of the trimmed circuits is comparable to that of untrimmed units.

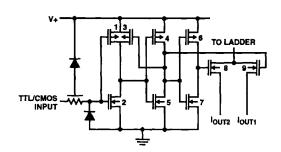

The level shifter circuits are comprised of three inverters with a positive feedback from the output of the second to first (Figure 1). This configuration results in TTL/COMS compatible operation over the full military temperature range. With the ladder SPDT switches driven by the level shifter, each switch is binary weighted for an "ON" resistance proportional to the respective ladder leg current. This assures a constant voltage drop across each switch, creating equipotential terminations for the 2R ladder resistor, resulting in accurate leg currents.

FIGURE 1. CMOS SWITCH

## Typical Applications

#### General Recommendations

Static performance of the AD7541 depends on  $I_{OUT1}$  and  $I_{OUT2}$  (pin 1 and pin 2) potentials being exactly equal to GND (pin3).

The output amplifier should be selected to have a low input bias current (typically less than 75nA), and a low drift (depending on the temperature range). The voltage offset of the amplifier should be nulled (typically less than ±200µV).

The bias current compensation resistor in the amplifier's non-inverting input can cause a variable offset. Non-inverting input should be connected to GND with a low resistance wire.

Ground-loops must be avoided by taking all pins going to GND to a common point, using separate connections.

The V+ (pin 18) power supply should have a low noise level and should not have any transients exceeding +17V.

Unused digital inputs must be connected to GND or V<sub>DD</sub> for proper operation.

A high value resistor  $({\sim}1 M\Omega)$  can be used to prevent static charge accumulation, when the inputs are open-circuited for any reason.

When gain adjustment is required, low tempco (approximately 50ppm/°C) resistors or trim-pots should be selected.

# Unipolar Binary Operation

The circuit configuration for operating the AD7541 in unipolar mode is shown in Figure 2. With positive and negative  $V_{\rm REF}$  values the circuit is capable of 2-Quadrant multiplication. The "Digital Input Code/Analog Output Value" table for unipolar mode is given in Table 1. A Schottky diode (HP5082-2811 or equivalent) prevents  $I_{\rm OUT_1}$  from negative excursions which could damage the device. This precaution is only necessary with certain high speed amplifiers.

FIGURE 2. UNIPOLAR BINARY OPERATION

(2-QUADRANT MULTIPLICATION)

#### **Zero Offset Adjustment**

- 1. Connect all digital inputs to GND.

- Adjust the offset zero adjust trimpot of the output operational amplifier for OV ±0.5mV (max) at V<sub>OUT</sub>.

#### **Gain Adjustment**

- 1. Connect all digital inputs to VDD

- 2. Monitor V<sub>OUT</sub> for a -V<sub>REF</sub> (1 1/2 12) reading.

- To increase V<sub>OUT</sub>, connect a series resistor, (0Ω to 250Ω), in the I<sub>OUT</sub>, amplifier feedback loop.

- 4. To decrease  $V_{OUT}$ , connect a series resistor,  $(0\Omega$  to 250 $\Omega$ ), between the reference voltage and the  $V_{REF}$  terminal.

TABLE 1. CODE TABLE - UNIPOLAR BINARY OPERATION

| DIGITAL INPUT | ANALOG OUTPUT                                            |

|---------------|----------------------------------------------------------|

| 11111111111   | -V <sub>REF</sub> (1 - 1/212)                            |

| 10000000001   | -V <sub>REF</sub> (1/2 + 1/2 12)                         |

| 10000000000   | -V <sub>REF</sub> /2                                     |

| 01111111111   | -V <sub>REF</sub> (1/ <sub>2</sub> - 1/ <sub>2</sub> 12) |

| 00000000001   | -V <sub>REF</sub> (1/212)                                |

| 00000000000   | 0                                                        |

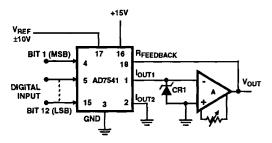

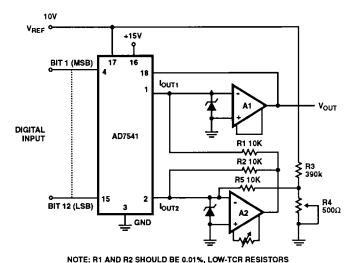

# Bipolar (Offset Binary) Operation

The circuit configuration for operating the AD7541 in the bipolar mode is given in Figure 3. Using offset binary digital input codes and positive and negative reference voltage values Four-Quadrant multiplication can be realized. The "Digital Input Code/Analog Output Value" table for bipolar mode is given in Table 2.

A "Logic 1" input at any digital input forces the corresponding ladder switch to steer the bit current to  $I_{OUT1}$  bus. A "Logic 0" input forces the bit current to  $I_{OUT2}$  bus. For any code the  $I_{OUT1}$  and  $I_{OUT2}$  bus currents are complements of one another. The current amplifier at  $I_{OUT2}$  changes the polarity of  $I_{OUT2}$  current and the transconductance amplifier at  $I_{OUT1}$  output sums the two currents. This configuration doubles the output range of the DAC. The difference current resulting at zero offset binary code, (MSB = "Logic 1", All other bits = "Logic 0"), is corrected by using an external resistive divider, from  $V_{\rm REF}$  to  $I_{\rm OUT2}$ .

#### Offset Adjustment

- 1. Adjust V<sub>REF</sub> to approximately +10V.

- 2. Set R4 to zero.

- 3. Connect all digital inputs to "Logic 1".

- Adjust I<sub>OUT1</sub> amplifier offset zero adjust trimpot for 0V ±0.1mV at I<sub>OUT2</sub> amplifier output.

- 5. Connect a short circuit across R2.

- 6. Connect all digital inputs to "Logic 0".

- Adjust I<sub>OUT2</sub> amplifier offset zero adjust trimpot for 0V±0.1mV at I<sub>OUT1</sub> amplifier output.

- 8. Remove short circuit across R2.

- 9. Connect MSB (Bit 1) to "Logic 1" and all other bits to "Logic 0".

- 10. Adjust R4 for 0V ±0.2mV at VOUT-

#### **Gain Adjustment**

- 1. Connect all digital inputs to VDD-

- 2. Monitor  $V_{OUT}$  for a - $V_{REF}$  (1  $^{1}/_{2}$   $^{11}$ ) volts reading.

- 3. To increase  $V_{OUT}$ , connect a series resistor,  $(0\Omega$  to  $250\Omega)$ , in the  $I_{OUT}$ 1 amplifier feedback loop.

- To decrease V<sub>OUT</sub>, connect a series resistor, (0Ω to 250Ω), between the reference voltage and the V<sub>REF</sub> terminal.

TABLE 2. CODE TABLE - BIPOLAR (OFFSET BINARY)

OPERATION

| DIGITAL INPUT | ANALOG OUTPUT                                                      |

|---------------|--------------------------------------------------------------------|

| 11111111111   | -V <sub>REF</sub> (1 - <sup>1</sup> / <sub>2</sub> <sup>11</sup> ) |

| 10000000001   | -V <sub>REF</sub> (1/211)                                          |

| 10000000000   | 0                                                                  |

| 01111111111   | V <sub>REF</sub> (1/211)                                           |

| 00000000001   | V <sub>REF</sub> (1 - 1/211)                                       |

| 00000000000   | V <sub>REF</sub>                                                   |

FIGURE 3. BIPOLAR OPERATION (4-QUADRANT MULTIPLICATION)

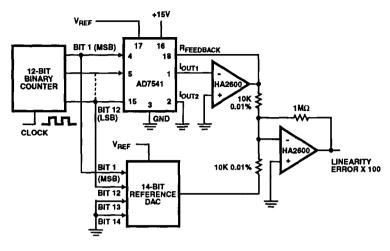

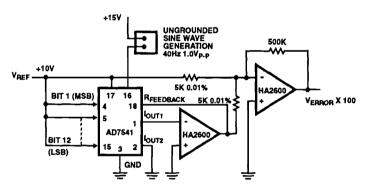

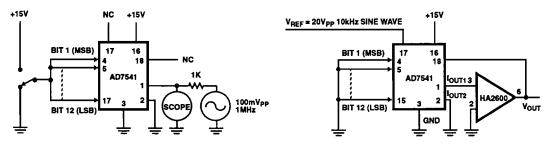

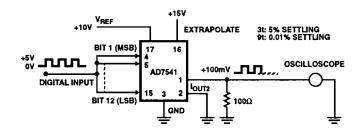

## Test Circuits

FIGURE 4. NONLINEARITY TEST CIRCUIT

FIGURE 5. POWER SUPPLY REJECTION TEST CIRCUIT

8-26

8

## Test Circuits (Continued)

FIGURE 7. OUTPUT CAPACITANCE TEST CIRCUIT

FIGURE 8. FEEDTHROUGH ERROR TEST CIRCUIT

FIGURE 9. OUTPUT CURRENT SETTLING TIME TEST CIRCUIT

## Dynamic Performance

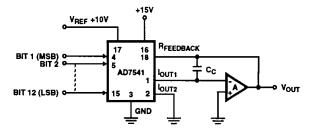

The dynamic performance of the DAC, also depends on the output amplifier selection. For low speed or static applications, AC specifications of the amplifier are not very critical. For high-speed applications slew-rate, settling-time, open-loop gain and gain/phase-margin specifications of the amplifier should be selected for the desired performance.

The output impedance of the AD7541 looking into  $I_{OUT1}$  varies between  $10k\Omega$  (R<sub>FEEDBACK</sub> alone) and  $5k\Omega$  (R<sub>FEEDBACK</sub> in parallel with the ladder resistance).

Similarly the output capacitance varies between the minimum and the maximum values depending on the input code. These variations necessitate the use of compensation capacitors, when high speed amplifiers are used.

A capacitor in parallel with the feedback resistor (as shown in Figure 10) provides the necessary phase compensation to critically damp the output.

A small capacitor connected to the compensation pin of the amplifier may be required for unstable situations causing oscillations. Careful PC board layout, minimizing parasitic capacitances, is also vital.

FIGURE 10. GENERAL DAC CIRCUIT WITH COMPENSATION CAPACITOR, Co.