D3111, APRIL 1988-REVISED AUGUST 1988

- IMPACT-X™ Technology with TTL I/O Compatibility

- 14 Bits Wide—Addresses Up to 16,384 Words of Microcode with One Chip

- Selects Address from One of Eight Sources

- Independent Read Pointer for Aid in Microcode Diagnostics

- Supports Real-Time Interrupts

- Two Independent Loop Counters

- Supports 64 Powerful Instructions

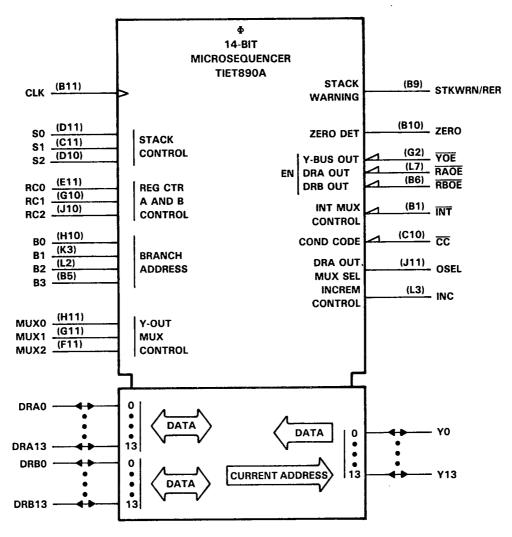

## description

The TIET890A is a powerful microsequencer that is implemented using Texas Instruments IMPACT-X™ technology providing ECL internal circuitry with TTL input and output compatibility. It is functionally equivalent to the SN74AS890 and requires a 5-volt power supply.

The microsequencer selects a 14-bit micro-address from one of eight sources to provide the proper microinstruction sequence for bit-slice processor or other microcode based systems. These high-performance devices are capable of addressing 16,384 control store memory locations either sequentially or via conditional branching algorithms. This multiway branching capability, coupled with a nine-word-deep LIFO (last in, first out) stack, allows the microprogrammer to arrange his code in blocks so that microprograms may be structured in the same fashion as such high-level languages as ALGOL, Pascal, or Ada.

Both polled and real-time interrupt routines are supported by the TIET890A to enhance system throughput capability. Vectored interrupts may occur during any instruction, including PUSHes and POPs.

Two 14-bit loadable registers/counters may be used for temporary storage of data or utilized as down counters for iterative instructions such as multiplication and division or as loop counters when iterative routines are required.

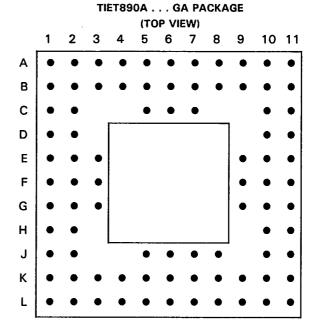

#### **TIET890A PIN ALLOCATIONS**

|     | PIN        |     | PIN             | Р   | IN    |

|-----|------------|-----|-----------------|-----|-------|

| NO. | NAME       | NO. | NAME            | NO. | NAME  |

| A1  | GND        | D1  | Y12             | J6  | Vcc   |

| A2  | DRB10      | D2  | Y9              | J7  | GND   |

| А3  | DRB9       | D10 | S2              | J8  | GND   |

| A4  | DRB8       | D11 | S0              | J10 | RC2   |

| A5  | DRB7       | E1  | Y11             | J11 | OSEL  |

| A6  | DRB6       | E2  | Y8              | K1  | Y1    |

| A7  | DRB5       | E3  | Vcc             | K2  | Y0    |

| A8  | DRB4       | E91 | Vcc             | кз  | В1    |

| A9  | DRB3       | E10 | NC              | K4  | DRA13 |

| A10 | DRB1       | E11 | RC0             | K5  | DRA11 |

| A11 | GND        | F1  | Y7              | К6  | DRA8  |

| B1  | DRB13      | F2  | GND             | K7  | DRA7  |

| B2  | ÎNT        | F3  | Vcc             | К8  | DRA0  |

| В3  | DRB12      | F9  | GND             | К9  | DRA1  |

| B4  | DRB11      | F10 | V <sub>CC</sub> | K10 | DRA3  |

| B5  | B3         | F11 | MUX2            | K11 | DRA2  |

| В6  | RBOE       | G1  | Y5              | L1  | GND   |

| B7  | DRB2       | G2  | YOE             | L2  | B2    |

| 88  | DRBO       | G3  | GND             | L3  | INC   |

| В9  | STKWRN/RER | G9  | Vcc             | L4  | DRA12 |

| B10 | ZERO       | G10 | RC1             | L5  | DRA10 |

| B11 | CLK        | G11 | MUX1            | L6  | DRA9  |

| C1  | Y13        | Н1  | Y4              | L7  | RAOE  |

| C2  | Y10        | H2  | Y6              | L8  | DRA6  |

| C5  | GND        | H10 | во              | L9  | DRA5  |

| C6  | VCC        | H11 | MUX0            | L10 | DRA4  |

| C7  | GND        | J1  | Y3              | L11 | GND   |

| C10 | CC         | J2  | Y2              |     |       |

| C11 | S1         | J5  | GND             |     |       |

IMPACT-X is a trademark of Texas Instruments Incorporated.

## description (continued)

An additional feature is a 4-bit port that appends four user-definable bits to the DRA or DRB address value for support of 16-way branches for the execution of relative branch addressing schemes.

The TIET890A is characterized for operation from 0°C to 70°C.

# logic symbol†

<sup>&</sup>lt;sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984.

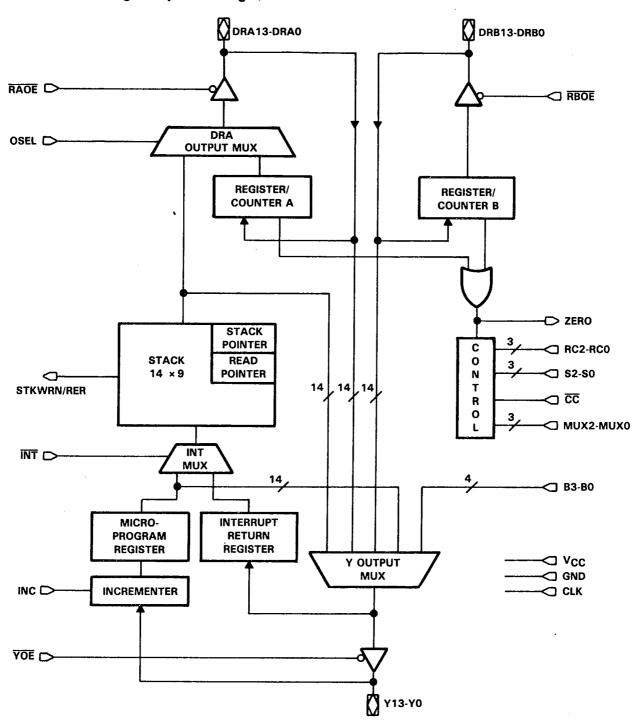

# functional block diagram (positive logic)

# TIET890A MICROSEQUENCER

| PIN   |         |     | DESCRIPTION                                                           |

|-------|---------|-----|-----------------------------------------------------------------------|

| NAME  | NO.     | I/O |                                                                       |

| B0    | H10     |     |                                                                       |

| B1    | К3      | 1   | Input bits for 16-way branch                                          |

| B2    | L2      |     |                                                                       |

| B3    | B5      |     |                                                                       |

| CC    | C10     | 1   | Condition code                                                        |

| CLK   | B11     | - 1 | Clock active on low-to-high transition                                |

| DRAO  | К8      |     |                                                                       |

| DRA1  | K9      |     |                                                                       |

| DRA2  | K11     |     |                                                                       |

| DRA3  | K10     |     |                                                                       |

| DRA4  | L10     |     |                                                                       |

| DRA5  | L9      |     |                                                                       |

| DRA6  | L8      | 1/0 | Bidirectional DRA data port                                           |

| DRA7  | K7      |     |                                                                       |

| DRA8  | K6      |     |                                                                       |

| DRA9  | L6      |     |                                                                       |

| DRA10 | L5      |     |                                                                       |

| DRA11 | K5      |     |                                                                       |

| DRA12 | L4      |     |                                                                       |

| DRA13 | К4      |     |                                                                       |

| DRBO  | B8      |     |                                                                       |

| DRB1  | A10     |     |                                                                       |

| DRB2  | B7      |     |                                                                       |

| DRB3  | A9      |     | ·                                                                     |

| DRB4  | A8      |     |                                                                       |

| DRB5  | A7      |     |                                                                       |

| DRB6  | A6      |     |                                                                       |

| DRB7  | A5      | I/O | Bidirectional DRB data port                                           |

| I .   |         |     |                                                                       |

| DRB8  | A4      |     |                                                                       |

| DRB9  | A3      |     |                                                                       |

| DRB10 | A2      |     |                                                                       |

| DRB11 | B4      |     |                                                                       |

| DRB12 | В3      |     |                                                                       |

| DRB13 | B1      |     |                                                                       |

| GND   | A1      |     | <b>,</b>                                                              |

| GND   | A11     |     |                                                                       |

| GND   | C5      |     | ·                                                                     |

| GND   | C7      |     |                                                                       |

| GND   | F2      |     |                                                                       |

| GND   | F9      |     | Ground pins. All pins must be used. J8 is internally connected to J7. |

| GND   | G3      |     |                                                                       |

| GND   | J5      |     |                                                                       |

| GND   | J7 (J8) |     |                                                                       |

| GND   | L1      |     |                                                                       |

| GND   | L11     |     |                                                                       |

| INC   | L3      | ı   | Incrementer control pin                                               |

| ĪNT   | B2      | 1   | Selects INT RT register to stack, active low                          |

| MUXO  | H11     |     |                                                                       |

| MUX1  | G11     | 1   | MUX control for Y output bus (See Table 1)                            |

| MUX2  | F11     |     |                                                                       |

| L     |         | L   | L                                                                     |

| <del></del>  |     | T        |                                                                        |

|--------------|-----|----------|------------------------------------------------------------------------|

| PIN          |     |          | DESCRIPTION                                                            |

| NAME         | NO. | 1/0      |                                                                        |

| OSEL<br>RAOE | J11 |          | MUX control for the source to DRA. Low selects RA, high selects stack. |

| RBOE         | L7  | <u> </u> | DRA output enable, active low                                          |

|              | B6  | 1        | DRB output enable, active low                                          |

| RC0          | E11 | ١.       |                                                                        |

| RC1          | G10 | 1        | Register/Counter controls (See Table 3)                                |

| RC2          | J10 |          |                                                                        |

| SO           | D11 |          |                                                                        |

| S1           | C11 | 1        | Stack control (See Table 2)                                            |

| S2           | D10 |          |                                                                        |

| STKWRN/RER   | B9  | 0        | Stack overflow, underflow/read error flag                              |

| vcc          | C6  |          |                                                                        |

| Vcc          | E3  |          |                                                                        |

| VCC          | E9  |          |                                                                        |

| Vcc          | F3  |          | 5-volt power supply                                                    |

| Vcc          | F10 |          |                                                                        |

| Vcc          | G9  |          |                                                                        |

| VCC          | J6  |          |                                                                        |

| YO           | K2  |          |                                                                        |

| Y1           | K1  |          |                                                                        |

| Y2           | K2  |          |                                                                        |

| Y3           | J1  |          |                                                                        |

| Y4           | H1  |          |                                                                        |

| Y5           | G1  |          | ·                                                                      |

| Y6           | H2  |          | Didinational V data as a                                               |

| Y7           | F1  | 1/0      | Bidirectional Y data port                                              |

| Y8           | E2  |          |                                                                        |

| Y9           | D2  |          |                                                                        |

| Y10          | C2  |          |                                                                        |

| Y11          | E1  |          |                                                                        |

| Y12          | D1  |          |                                                                        |

| Y13          | C1  |          |                                                                        |

| YOE          | G2  |          | Y output bus enable, active low                                        |

| ZERO         | B10 |          | Zero detect flag for register A and B                                  |

#### PRINCIPLES OF OPERATIONS

## Y output multiplexer

The Y output multiplexer of the TIET890A is capable of selecting the next branch address from one of eight locations. Addresses may be sourced from:

- 1. The top of the 14-bit by 9-word address stack

- 2. An external input on the DRA port, potentially a pipeline register

- 3. An external input on the DRB port, potentially a pipeline register

- 4. Internal register/counter A

- 5. Internal register/counter B

- 6. An internal microprogram counter (MPC register)

- 7. An external input onto the bidirectional Y output port

- 8. A 16-way branch—4 bits appended to DRA, DRB, register/counter A or register/counter B.

The source of the next address is dependent upon the previous state of the microsequencer, the MUX controls (MUX2-MUX0), the condition code (CC) input, and the state of an internal status flag (status externally available at the ZERO output) that indicates that one of the on-chip registers is being decremented to zero.

The entire instruction set may be made conditional by manipulation of the condition code (CC) input. Allowing the CC value to vary as a result of data or status provides for state-dependent or data-dependent branching. Unconditional branches may be achieved by forcing CC high when selecting control store addresses. Holding this pin low will provide for conditional or unconditional branches as dictated by the state of the zero-detect flag. The required control signals for selection of the Y output source are listed in Table 1. Note that the dependence of the TIET890A on two variables for conditional branches and jumps allows a conditional branch or conditional jump to subroutine in any clock cycle. Also note that all multiplexer inputs are overridden when all of the stack control inputs are pulled low. This instruction resets the stack and read pointers to zero and places all lines of the Y output bus at the low level.

TABLE 1. Y OUTPUT CONTROL

| MUX CONTROL |           | <u> </u> | Y OUTPUT SOURCE |                      | Y OUTPUT SOURCE |                      |  |

|-------------|-----------|----------|-----------------|----------------------|-----------------|----------------------|--|

|             | 0.01111/4 |          | RESET*          | <u>CC</u> = L        |                 | CC = H               |  |

| MUXZ        | MUX1      | MUXU     | ]               | ZERO = L             | ZERO = H        |                      |  |

| Х           | Х         | Х        | YES             | ALL LOW              | ALL LOW         | ALL LOW              |  |

| L           | L         | L        | NO              | STK                  | MPC             | DRA                  |  |

| L           | L         | Н        | NO              | STK                  | MPC             | DRB                  |  |

| L           | Н         | L        | NO              | STK                  | DRA             | MPC                  |  |

| L           | н         | н        | NO              | STK                  | DRB             | MPC                  |  |

| н           | L         | L        | NO              | DRA                  | MPC             | DRB                  |  |

| н           | L         | н        | NO              | DRA' (16-WAY BRANCH) | MPC             | DRB' (16-WAY BRANCH) |  |

| н           | н         | L        | NO              | DRA                  | STK             | MPC                  |  |

| н           | н         | Н        | NO              | DRB                  | STK             | MPC                  |  |

H = high level, L = low level, X = irrelevant.

<sup>\*</sup>Reset command is implemented by setting S2-S0 = LLL.

## 14-bit by 9-word address stack

The positive-edge-triggered 14-bit address stack supplies on-board storage of nine control store addresses that support up to nine nested levels of microsubroutine, looping, and real-time interrupt functions. The stack pointer (SP), which operates as an up-down counter, is updated after the execution of each PUSH operation and before each POP. In a PUSH operation, the address stored in the selected register (either MPC or INT RT) is loaded into the stack location addressed by the stack pointer, and the stack pointer is incremented. This address is available at the DRA port by enabling DRA (RAOE low and OSEL high).

A POP operation causes the stack pointer to be decremented on the first rising clock edge following the arrival of the POP instruction at the S2-S0 pins. The value that was indexed by the stack pointer is effectively removed from the top of the stack. All PUSH and POP instructions are conditionally dependent upon the stack control inputs (S2-S0), the condition code ( $\overline{CC}$ ), the input value, and the zero-detect status. The desired option may be selected using the stack control inputs listed in Table 2.

| STACK      | CON | TROL |      | STACK OPERA  |             |             |

|------------|-----|------|------|--------------|-------------|-------------|

| <b>S</b> 2 | S1  | SO   | OSEL | ZERO - L     | ZERO - H    | CC = H      |

| L          | L   | L    | X    | RESET/CLEAR  | RESET/CLEAR | RESET/CLEAR |

| L          | L   | Н    | X    | CLEAR SP, RP | HOLD        | HOLD        |

| L          | Н   | L    | Х    | HOLD         | POP         | POP         |

| L          | Н   | Н    | Х    | POP          | HOLD        | HOLD        |

| н          | L   | L    | ×    | HOLD         | PUSH        | PUSH        |

| Н          | L   | Н    | X    | PUSH         | HOLD        | HOLD        |

| Н          | Н   | L    | Х    | PUSH         | HOLD        | PUSH        |

| н          | Н   | Н    | н    | READ         | READ        | READ        |

| Н          | Н   | н    | L    | HOLD         | HOLD        | HOLD        |

**TABLE 2. STACK CONTROL**

The read pointer (RP) is a useful tool in debugging microcoded systems. A microprogrammer now has the ability to perform a nondestructive, sequential read of the stack contents from the DRA port. This capability provides the user with a method of backtracking through the address sequence to determine the cause of overflow without affecting program flow, the status of the stack-pointer or the internal data of the stack. Placing a high value on all of the stack inputs (S2-S0) and OSEL places the TIET890A into the read mode. At each low-to-high clock transition, the value pointed to by the read pointer is available at the DRA port and the read pointer is decremented. Microcode diagnostics are simplified by the ability of the TIET890 to sequentially dump the contents of its stack. The bottom of the stack is detected by monitoring the STKWRN/RER (stack warning/read error) pin. A high will appear when the stack contains one word and a READ instruction is applied to the S2-S0 pins. This signifies that the last address has been read. The stack pointer and stack contents are unaffected by the READ operation. Under normal PUSH and POP operations the read pointer is updated with the stack pointer and contains identical information.

The STKWRN/RER pin alerts the system to a potential stack overflow or underflow condition. STKWRN/RER becomes active under two additional conditions. If seven of the nine stack locations (0-8) are full (the stack pointer is at 7) and a PUSH occurs, the STKWRN/RER pin will produce a high-level signal to warn that the stack is approaching its capacity, and will be full after one more PUSH. Knowledge that overflow potential exists allows bit-slice-based systems to continuously process real-time interrupt vectors. This signal will remain high, if HOLD, PUSH, or POP instructions occur, until the stack pointer is decremented to 7.

The user may be protected from attempting to POP an empty stack by monitoring STKWRN/RER before POP operations. A high level at this pin signifies that the last address has been removed from the stack (SP=0). This condition remains until an address is pushed onto the stack and the stack pointer is incremented to one.

Clearing the stack and read pointer is accomplished by placing low levels onto the stack control lines (S2-S0). This function overrides all of the Y output MUX controls and places the Y bus into a low state.

1

## register/counters

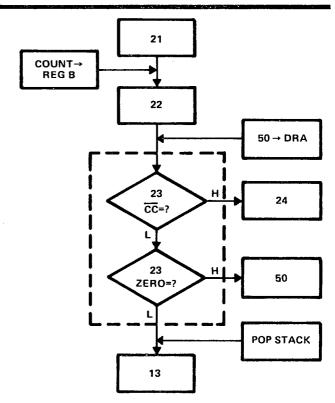

Two loadable 14-bit registers extend the looping and branching capabilities. Addresses may be loaded directly into register/counter A (RA) and register/counter B (RB) through the direct data ports DRA13-DRA0 and DRB13-DRB0. The values stored in these registers may either be held, decremented, or read as a result of the register control inputs (RC2-RC0), RAOE, and RBOE. All combinations of these functions are supported with the exception of a simultaneous decrement of both registers. Generation of iteration routines may be accomplished by loading RA and/or RB and operating them as a down counter. Loop termination is acknowledged by the ZERO output going high to indicate that a register contains a binary one and that a decrement is about to take place. Because of this facility, a "decrement and branch on loop termination" may be executed in the same clock cycle.

The contents of RA are accessible to the DRA port when OSEL is low and the output bus is enabled by RAOE being low. Data from RB is available when DRB is enabled by RBOE being low. Note that control of the registers is maintained while an external value is active on the DRA and DRB ports. A value being directed from the DRA and DRB buses to the output will not inhibit the decrement operation.

Register/counter controls are listed in Table 3.

**REG B** RC2 RC1 **RCO REG A** L L L HOLD HOLD DEC HOLD L L Н LOAD HOLD L Н L DEC LOAD L Н Н LOAD LOAD L Н L Н HOLD DEC Н Н L HOLD LOAD DEC LOAD Н Н

**TABLE 3. REGISTER CONTROL**

#### microprogram register and increment

The microprogram register (MPC) and the incrementer (INC) provide the means for generating the next microprogram address for sequential addressing operations. The MPC may be loaded with either the outgoing address on the Y bus or may receive an external address for processing interrupt vectors.

The current address on the Y bus is passed to the MPC at each rising clock edge, either unaltered (INC low) for repeating statements, or incremented by one (INC high) for addressing sequential control store locations.

The MPC may also be externally loaded for subroutine and interrupt functions. Taking YOE high and forcing the new address onto the bidirectional Y bus loads the MPC with the new address at the positive clock edge. This value may also be incremented prior to storage in the MPC for sequential addressing of subroutines or interrupt routines.

#### interrupts

Real-time vectored interrupt routines are supported for those applications where polling would impede system throughput. Any instruction, including PUSHes and POPs, may be interrupted. To process an interrupt, the following procedure should be followed:

- 1. The bidirectional Y bus is placed into the high-impedance state by forcing YOE high.

- 2. The interrupt entry point vector is then forced onto the Y bus and incremented to become the second microinstruction of the interrupt routine. This is accomplished by making INC high.

3. At the following clock edge, the second microaddress is stored in the MPC and the interrupted address will be stored in the INT RT register which always contains the outgoing value from the Y mux. This edge also causes the processor to begin execution of the first instruction of the interrupt routine. This first instruction must PUSH the address stored in the INT RT register onto the stack so that the proper return linkage is maintained. This is accomplished by making INT low and performing a PUSH. If this instruction were to be interrupted, the process would be repeated and the proper return linkage preserved.

#### control inputs

A listing of the response of internal elements to various control inputs is given in Table 4.

**LOGIC LEVEL PIN NAME** HIGH LOW RACE DRA output in high-Z state DRA output is active **RBOE** DRB output in high-Z state DRB output is active YOE Y output in high-Z state Y output is active INT MPC to stack INT RT register to stack OSEL Stack to DRA buffer input RA to DRA buffer input INC Adds one to Y output and stores in MPC Passes Y output to MPC unaltered MUX2-MUX0 Table 1 Table 1 S2-S0 Table 2 Table 2 Table 3 RC2-RC0 Table 3

**TABLE 4. RESPONSE TO CONTROL INPUTS**

#### instruction set

Sixty-four microsequencing instructions enable the TIET890A to generate micro-addresses for up to 16,384 locations. Any instruction can be made conditional depending upon the value of the externally applied condition code  $(\overline{CC})$  and the value stored in either of the internal register/counters.

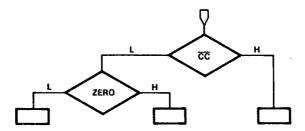

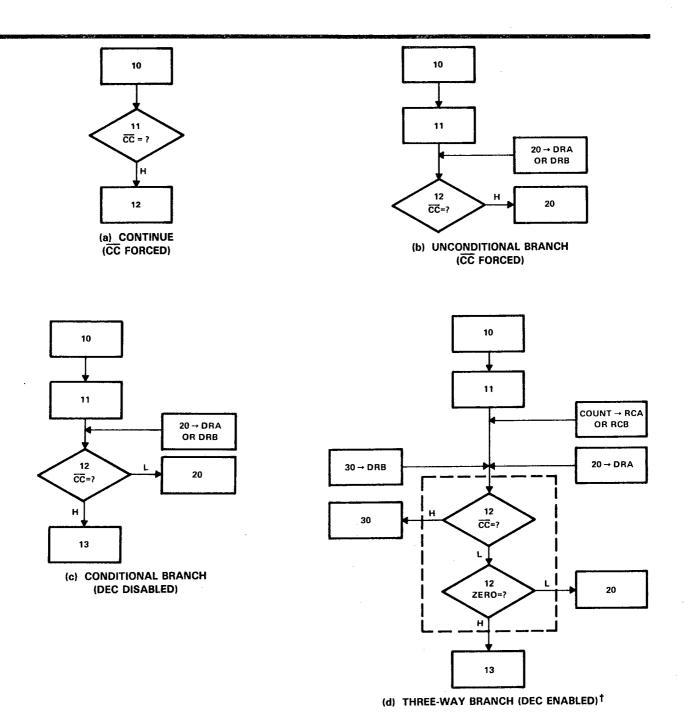

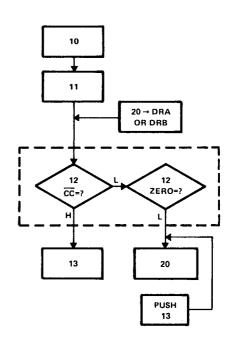

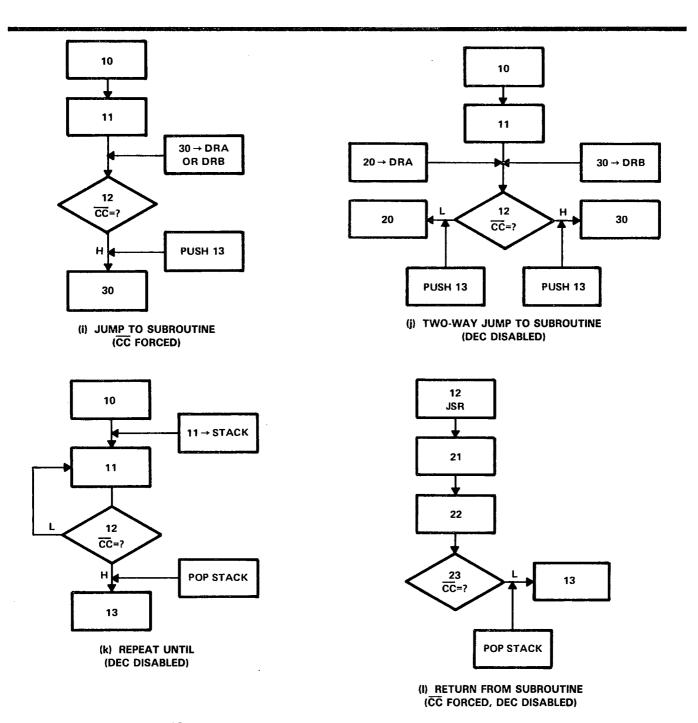

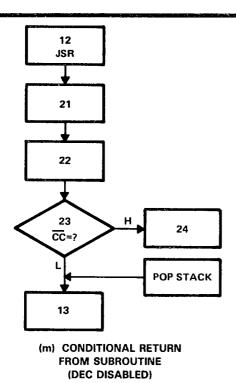

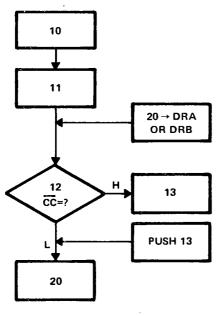

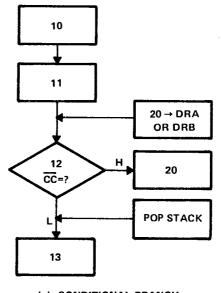

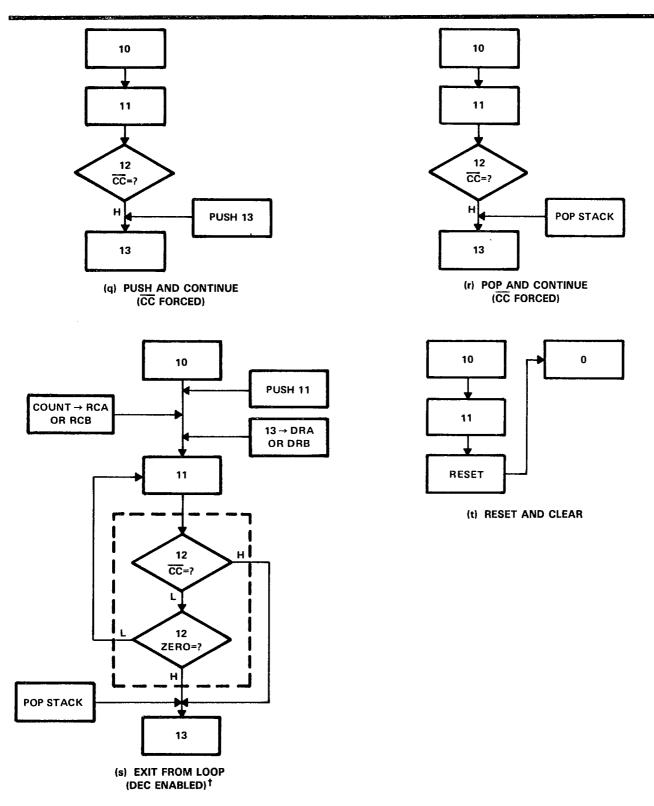

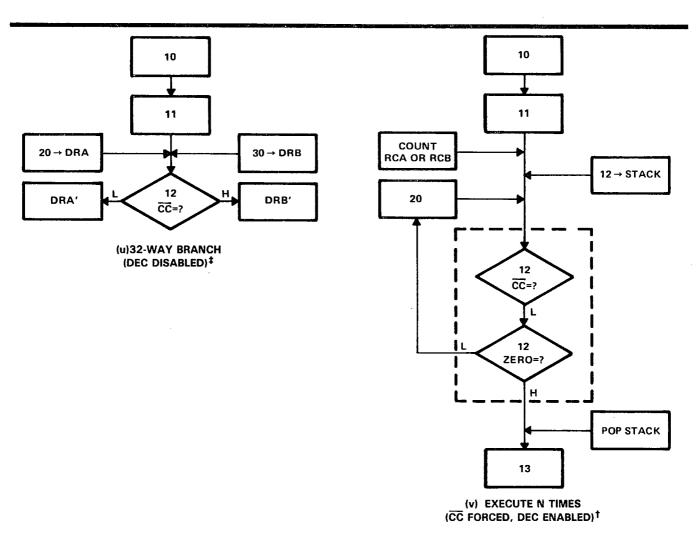

The required signals for selection of the Y output source were listed in Table 1. Suggested methods for implementing a few commonly used instructions are given in Table 5 and flowcharts showing execution examples are illustrated in Figure 1.

It should be noted that the term jump refers to a subroutine call that must be accompanied by a return instruction. The term branch implies that a deviation from the program flow is accomplished but no return is required.

TABLE 5. SUGGESTED CODING FOR REPRESENTATIVE INSTRUCTIONS

| FUNCTION                                     | MNEMONIC | MUX2 | MUX1 | MUXO | <b>S2</b> | S1 | SO | CC | FIGURE |

|----------------------------------------------|----------|------|------|------|-----------|----|----|----|--------|

| Continue                                     | CONT     | Х    | Н    | Х    | H         | Н  | Н  | Н  | 1 (a)  |

| Unconditional branch                         | BR       | L    | l L  | х    | Н         | Н  | Н  | Н  | 1 (b)  |

| Conditional branch                           | CBR      | Н    | Н    | х    | н         | Н  | н  | ٧  | 1 (c)  |

| Three-way branch                             | BR2W     | Н    | L    | L    | н         | Н  | н  | ٧  | 1 (d)  |

| Conditional loop on stack                    | LOOPS    | L    | L    | х    | L         | Н  | L  | L  | 1 (e)  |

| Repeat                                       | REPEAT   | L    | L    | х    | н         | н  | Н  | L  | 1 (f)  |

| Loop on stack with exit                      | LSWE     | L    | L    | х    | L         | Н. | L  | ٧  | 1 (g)  |

| Conditional jump to subroutine               | CJSR     | н    | н    | x    | н         | L  | н  | V  | 1(h)   |

| Jump to subroutine                           | JSR      | L    | L    | x    | н         | L  | н  | Н  | 1 (i)  |

| Two-way jump to subroutine                   | JSR2W    | н    | L    | L    | Н         | н  | 니니 | ٧  | 1 (j)  |

| Repeat until                                 | UNTIL    | L    | Н :  | х    | L         | н  | ᅵᅵ | V  | 1(k)   |

| Return from subroutine                       | RTS      | L    | н    | х    | L         | н  | н  | L  | 1 (I)  |

| Conditional return from subroutine           | CRTS     | L    | Н    | х    | L         | н  | н  | V  | 1 (m)  |

| Conditional return from subroutine or branch | CRTSB    | L    | н    | х    | L         | н  | н  | V  | 1 (n)  |

| Conditional branch and PUSH                  | CBRP     | н    | н    | х    | н         | L  | н  | V  | 1 (o)  |

| Conditional branch and POP                   | CBRPO    | н    | н    | x    | L         | н  | н  | V  | 1 (p)  |

| PUSH and continue                            | PUSH     | L    | н    | x    | н         | L  | L  | Н  | 1(q)   |

| POP and continue                             | POP      | х    | н    | х    | L         | н  | L  | Н  | 1 (r)  |

| Exit from loop                               | EXITLP   | L    | L    | х    | L         | н  | L  | V  | 1 (s)  |

| Reset and clear stack/read pointer           | RESET    | х    | х    | x    | L         | L  | L  | X  | 1 (t)  |

| 32-way branch                                | BR32W    | н    | L    | н    | Н         | н  | н  | V  | 1(u)   |

| Execute n times                              | NEX      | L    | L    | х    | L         | н  | L  | L  | 1(v)   |

H = high level, L = low level, X = irrelevant, V = varies (condition code value is dependent upon machine and data status and will vary accordingly).

${}^{\dagger}\overline{CC}$  and ZERO are completed in the same clock cycle.

FIGURE 1. INSTRUCTION SET FLOWCHARTS

# TIET890A **MICROSEQUENCER**

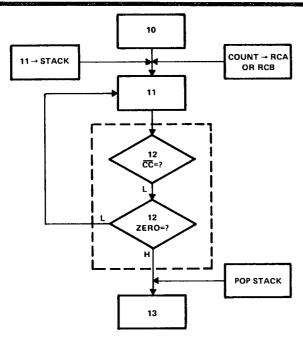

(e) CONDITIONAL LOOP ON STACK (CC FORCED, DEC ENABLED)†

(f) REPEAT (CC FORCED, DEC DISABLED)†

(g) CONDITIONAL LOOP ON STACK WITH EXIT (DEC ENABLED)†

(h) CONDITIONAL JUMP TO SUBROUTINE (DEC DISABLED)†

†CC and ZERO are completed in the same clock cycle.

FIGURE 1. INSTRUCTION SET FLOWCHARTS (continued)

FIGURE 1. INSTRUCTION SET FLOWCHARTS (continued)

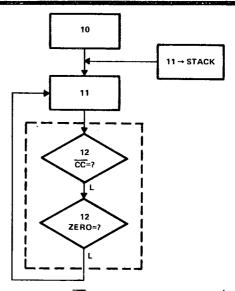

(n) CONDITIONAL RETURN FROM SUBROUTINE OR BRANCH (DEC ENABLED)†

(o) CONDITIONAL BRANCH AND PUSH (DEC DISABLED)

(p) CONDITIONAL BRANCH AND POP (DEC DISABLED)

†CC and ZERO are completed in the same clock cycle.

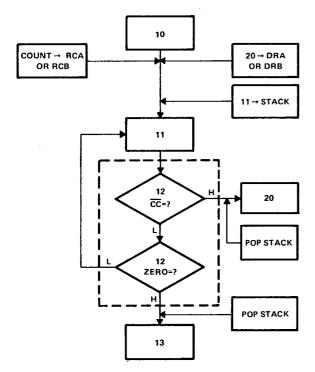

FIGURE 1. INSTRUCTION SET FLOWCHARTS (continued)

$^{\dagger}\overline{\text{CC}}$  and ZERO are completed in the same clock cycle.

FIGURE 1. INSTRUCTION SET FLOWCHARTS (continued)

†CC and ZERO are completed in the same clock cycle.

FIGURE 1. INSTRUCTION SET FLOWCHARTS (concluded)

<sup>&</sup>lt;sup>‡</sup>The least significant four bits, DRA and DRB, will be stripped off and four new bits appended to them from the B3-B0 port.

| Supply voltage, VCC                      |

|------------------------------------------|

| Input voltage: I/O ports                 |

| All other inputs                         |

| Operating case temperature range         |

| Storage temperature range65 °C to 150 °C |

# recommended operating conditions (see Note 1)

TEXAS INSTR {UC/UP} Ob

|     | PARAMETER                      | MIN N | OM MAX | UNIT |

|-----|--------------------------------|-------|--------|------|

| VCC | I/O supply voltage             | 4.5   | 5 5.5  | V    |

| VIH | High-level input voltage       | 2     |        | V    |

| VIL | Low-level input voltage        |       | 0.8    | V    |

| ЮН  | High-level output current      |       | -2.6   | mA.  |

| lOL | Low-level output current       |       | 24     | mΑ   |

| ΤΔ  | Operating free air temperature | 0     | 70     | °C   |

NOTE 1: The specified limits shown apply only after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 2.5 meters/s (500 ft/min) is maintained.

# electrical characteristics over recommended conditions (unless otherwise noted)

|      | PARAMETER                             | TEST CONDI                                  | TIONS                      | MIN T              | γP <sup>†</sup> | MAX   | UNIT     |

|------|---------------------------------------|---------------------------------------------|----------------------------|--------------------|-----------------|-------|----------|

| VIK  |                                       | $V_{CC} = 4.5 \text{ V},$                   | I <sub>I</sub> = -18 mA    |                    |                 | -1.2  | V        |

|      |                                       | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V},$ | $I_{OH} = -0.4 \text{ mA}$ | V <sub>CC</sub> -2 |                 |       | V        |

| Vон  |                                       | $V_{CC} = 4.5 \text{ V},$                   | $I_{OH} = -2.6 \text{ mA}$ | 2.4                | 3.2             |       | <u> </u> |

| VOL  |                                       | $V_{CC} = 4.5 V$ ,                          | IOL = 24 mA                | (                  | 0.35            | 0.5   | V        |

|      | All inputs except RAOE, RBOE, and YOE | V <sub>CC</sub> = 5.5 V,                    | V <sub>I</sub> = 7 V       |                    |                 | 0.1   | mA       |

| lį.  | RAOE, RBOE, and YOE                   | $V_{CC} = 5.5 V,$                           | V <sub>I</sub> = 7 V       |                    |                 | 0.2   | 1111/4   |

|      | I/O ports                             | V <sub>CC</sub> = 5.5 V,                    | $V_{ } = 5.5 V$            |                    |                 | 0.1   |          |

|      | All inputs except                     |                                             |                            |                    |                 | 20    |          |

| lн‡  | RAOE, RBOE, and YOE                   | $V_{CC} = 5.5 V,$                           | $V_1 = 2.7 \text{ V}$      |                    |                 |       | μΑ       |

| יווי | I/O ports,                            | VCC = 3.5 V,                                | V <sub>1</sub> - 2.7 V     |                    | 40              |       | "'`      |

|      | RAOE, RBOE, and YOE                   |                                             |                            | .,                 |                 |       |          |

| կլ‡  | RAOE, RBOE, and YOE                   | $V_{CC} = 5.5 V_{r}$                        | $V_1 = 0.4 \text{ V}$      |                    |                 | -400  | μА       |

| !    | All other inputs and I/O              | VCC = 5.5 V,                                | ·   - 0.3 V                |                    |                 | - 200 |          |

| lo§  |                                       | $V_{CC} = 5.6 V$ ,                          | $V_0 = 2.25 V$             | -30                |                 | -112  | mA       |

| lcc  |                                       | V <sub>CC</sub> = 5.5 V                     |                            |                    | 650             | 725   | mA       |

<sup>&</sup>lt;sup>†</sup> All typical values are for  $V_{CC} = 5 \text{ V}$  and  $T_A = 25 ^{\circ}\text{C}$ .

<sup>‡</sup> For I/O ports, the parameters I<sub>IH</sub> and I<sub>IL</sub> include the output buffer off-state current.

<sup>§</sup> The output conditions for IO have been selected to produce a current that closely approximates one-half of the true short-circuit current, IOS.

# maximum switching characteristics over recommended operating ranges of temperature and supply voltages (see Note 2)

| PARAMETER        | FROM       |                 |                 | FO (OUT | PUT)     |        | LIND |  |

|------------------|------------|-----------------|-----------------|---------|----------|--------|------|--|

| TANAMETER        | (INPUT)    | Y               | ZERO            | DRA     | DRB      | STKWRN | UNIT |  |

|                  | CC         | 16              |                 |         |          |        |      |  |

|                  | CLK        | 15              |                 | 15      | 11       | 12     |      |  |

|                  |            | 19 <sup>†</sup> | 15 <sup>†</sup> |         |          |        |      |  |

|                  | DRA13-DRA0 | 14              |                 |         |          | -      |      |  |

| • .              | DRB13-DRB0 | 14              | <del></del>     |         |          |        | ns   |  |

| <sup>t</sup> pd  | MUX2-MUX0  | 15              | -               |         |          |        |      |  |

|                  | RC2-RC0    | 19              | 12              |         |          |        |      |  |

| Γ                | \$2-\$0    | 18              | *****           |         |          |        |      |  |

| Γ                | B2-B0      | 12              |                 |         |          |        |      |  |

|                  | OSEL       |                 |                 | 15      |          |        |      |  |

|                  | YOE        | 10              |                 |         |          |        |      |  |

| t <sub>en</sub>  | RAOE       |                 |                 | 12      |          |        | ns   |  |

|                  | RBOE       |                 | ·               |         | 11       |        |      |  |

|                  | YOE        | 11              |                 |         | <u>.</u> |        |      |  |

| <sup>t</sup> dis | RAOE       |                 |                 | 6       |          |        | ns   |  |

|                  | RBOE       |                 |                 |         | 6        |        |      |  |

<sup>&</sup>lt;sup>†</sup>Decrementing Register/Counter A or B and sensing a zero.

NOTE 2: For load circuit and voltage waveforms, see page 1-12 of The TTL Data Book, Volume 3, 1984.

## setup and hold times

| PARAMETER                   | FROM        | TO (DESTINATION) | MIN | MAX | UNIT |

|-----------------------------|-------------|------------------|-----|-----|------|

|                             | CC          | Stack            | 10  |     |      |

|                             | DRA13-DRA0  | RCA              | 3   |     |      |

|                             | DRA 13-DRAO | INT RT           | 7   | • • |      |

|                             | DRB13-DRB0  | RCB              | 4   |     |      |

|                             | DRB13-DRB0  | INT RT           | 7   |     |      |

|                             | INC         | MPC              | 4   |     |      |

|                             | INT         | Stack            | 9   |     |      |

| t <sub>su</sub> before CLK↑ |             | Stack            | 8   |     | กร   |

|                             | RC2-RC0     | RCA, RCB         | 6   |     |      |

|                             |             | INT RT           | 6   |     |      |

|                             | 60.60       | Stack            | 11  |     |      |

|                             | S2-S0       | INT RT           | 9   |     |      |

|                             | MUX2-MUX0   | INT RT           | 11  |     |      |

|                             | B3-B0       | INT RT           | 12  |     |      |

|                             | Y13-Y0      | MPC              | 5   |     |      |

|                             | DRA         | RCA              | 1   |     |      |

| t <sub>h</sub> after CLK↑   | DRB         | RCB              | 1   |     |      |

| th alter CENT               | Υ           | MPC              | 1   |     | ns   |

|                             | All other   | Any Destination  | 0   |     |      |

# minimum clock requirements (see Note 3)

|                 | PARAMETER                  | MIN MA | X UNIT |

|-----------------|----------------------------|--------|--------|

| twL             | Pulse duration, clock low  | 6      |        |

| t <sub>wH</sub> | Pulse duration, clock high | 7      | ns     |

| t <sub>C</sub>  | Clock cycle time           | 20     |        |

NOTE 3: The total clock period of clock high and clock low must not be less than clock cycle time. The minimum pulse durations specified are only for clock high or clock low, but not for both simultaneously.